2016年8月

Journal of Terahertz Science and Electronic Information Technology

Aug., 2016

文章编号: 2095-4980(2016)04-0647-06

# 一种基于半监督 AdaBoost 模型树的 FPGA 性能表征方法

杨立群 1,2,李 威1,黄志洪1,孙嘉斌1,杨海钢1

(1.中国科学院电子学研究所 可编程芯片与系统研究室, 北京 100190; 2.中国科学院大学, 北京 100049)

摘 要:提出了一种基于半监督自适应增强(AdaBoost)模型树的建模方法,用于现场可编程门阵列(FPGA)的性能表征。该方法以半监督学习方式,构建了FPGA性能关于FPGA架构参数的解析模型,同时采用AdaBoost算法提高FPGA性能模型的预测精确度。使用VTR(Verilog To Routing)电路集,基于该方法构建的性能模型在预测FPGA上实现的应用电路面积时,平均相对误差(MRE)为4.42%;预测延时的MRE为1.63%;预测面积延时积时,MRE为5.06%。与全监督模型树算法以及现有的半监督模型树算法相比较,该方法构建的FPGA实现面积模型的预测精确度分别提高了39%,26%。实验结果显示,该方法在确保较少的时间开销前提下,构建了具有高预测精确度的FPGA性能模型,提供了一种高效的FPGA性能表征方法。

关键词: FPGA 性能表征; 半监督模型树; AdaBoost 模型树

中图分类号: TN409

文献标识码:A

doi: 10.11805/TKYDA201604.0647

# An FPGA performance characterization approach based on semi-supervised AdaBoost model tree

YANG Liqun<sup>1,2</sup>, LI Wei<sup>1</sup>, HUANG Zhihong<sup>1</sup>, SUN Jiabin<sup>1</sup>, YANG Haigang<sup>1</sup>

(1.System on Programmable Chip Research Department, Institute of Electronics, Chinese Academy of Sciences, Beijing 100190, China;

2.University of Chinese Academy of Sciences, Beijing 100049, China)

Abstract: A semi-supervised Adaptive Boosting(AdaBoost) model tree based modeling approach is proposed for Field Programmable Gate Array(FPGA) performance characterization. The proposed approach, which adopts AdaBoost to improve the prediction accuracy, constructs an analytical performance model with regard to the FPGA architecture parameters in semi-supervised learning way. The FPGA performance model built through the proposed approach estimates the area, delay and area-delay product with Mean Relative Errors(MREs) of 4.42%, 1.62% and 5.06%, respectively. Compared to the supervised model tree and the previous semi-supervised model tree algorithm, the proposed approach boosts the estimation accuracy by 39% and 26% respectively. Experimental results show that the proposed approach is proved to be an efficient FPGA characterization approach, building FPGA performance models with high accuracy in less time cost. The proposed modeling approach can be applied to explore the FPGA architecture design space effectively and efficiently.

Key words: FPGA performance characterization; semi-supervised model tree; AdaBoost model tree

自 1984 年第一款现场可编程门阵列(FPGA)芯片 XC2064 问世以来,每一代 FPGA 的系统容量与性能得益于工艺的进步,有大幅度的提升。为更好地满足工艺进步带来的市场需求,FPGA 需要在较短的开发周期内完成高性能的芯片开发。除了高效的 FPGA 电路级以及物理级设计以外,还需要加速 FPGA 设计初期的架构选择过程,以满足快速的面市需求。FPGA 架构指其内部可编程逻辑与互连的结构<sup>[1]</sup>,可由一系列 FPGA 架构参数进行表征。FPGA 架构对在其上实现的应用电路的性能(如面积、延时和面积延时积等)有较大影响。随着 FPGA 以及各领域应用的发展,需要考虑的架构参数不断增多。如何从快速增长的 FPGA 架构空间中选择满足设计指标(面积、延时等)的优化架构是 FPGA 设计初期需要解决的关键问题。高效的 FPGA 架构性能表征方法可有效解决这个问题。

**收稿日期**: 2014-10-28; **修回日期**: 2015-01-04 **基金项目**: 国家自然科学基金资助项目(61271149)

Yang<sup>[2]</sup>等人提出一种半监督模型树方法(Semi-supervised Model Tree, SMT),构建 FPGA 架构性能关于 FPGA 架构参数的解析模型。针对基于 CAD 流程获得 FPGA 架构性能时间开销较大的问题,其采用半监督学习方式。基于有限的获得性能的 FPGA 架构,构建初始性能模型,通过开发更多的未获得性能的 FPGA 架构,精炼和优化 FPGA 性能模型。该方法解决了传统 FPGA 架构开发中的时间开销问题,并能获得关于 FPGA 架构参数的显示性能模型,指导 FPGA 设计师对架构参数进行设计折中。

本文在 SMT 方法进行 FPGA 性能建模的思想基础上,开发了一种半监督自适应增强模型树(Semi-supervised AdaBoost Model Tree,SAMT)算法,用于对 FPGA 架构性能进行表征。采用自适应增强(AdaBoost)方式提升了 FPGA 性能模型预测精确度。将 SAMT 与全监督模型树算法以及 SMT 算法进行对比,进一步验证了本文方法用于 FPGA 架构性能表征的高效性。

#### 1 SAMT 算法原理及步骤

#### 1.1 AdaBoost 简介

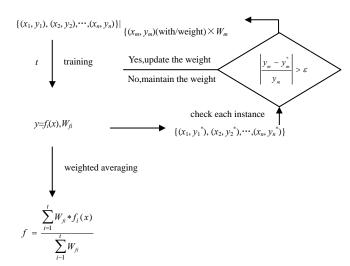

Schapire 最初于 1990 年提出增强(boosting)算法的概念<sup>[3]</sup>,由于其需要大量的训练数据,因此在实际应用中受到限制。Freund 和 Schapire 于 1997 年提出的 AdaBoost 算法有效克服了这一限制<sup>[4]</sup>,其通过数据子集采样或者数据重新分配权重的方式,充分利用有限的训练数据训练模型。最初 AdaBoost 算法只用于二值分类问题,Freund和 Schapire 后来对其进行扩展,使得其可以解决具有多响应数据的分类问题<sup>[5]</sup>。而后,Freund和 Schapire 又继续扩展原来的算法,使得其可以解决数据拟合问题,开发了 AdaBoost.R 算法。Solomatine和 Shrestha在此基础上开发了 AdaBoost.RT 算法<sup>[6]</sup>。AdaBoost 由于其坚实的理论基础、精确的预测能力、简单的实现方式得到了广泛应用<sup>[7]</sup>。AdaBoost 通过结合预测性能较差的"弱"模型,得到"强"模型。本文采用基于数据重新分配权重方式的

AdaBoost 算法,其用于解决拟合问题的思路如图 1 所示。

AdaBoost 根据带有权重的数据样本训练弱模型  $f_i(x)$ 并得到该模型的权重  $W_{fi}$ ,用  $f_i(x)$ 预测数据样本,加大预测误差超出阈值  $\varepsilon$  的样本权重,使得在下一次的学习中,模型能够对该预测误差较大的样本进行增强学习,这一过程迭代 t 次,即训练 t 个弱模型。最后对得到的 t 个弱模型进行加权平均得到最终的模型。

#### 1.2 SAMT 对 FPGA 性能建模过程

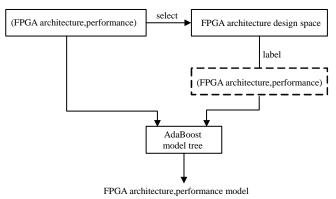

本文基于 AdaBoost 算法原理,提出 SAMT 算法对 FPGA 性能进行建模,建模过程如图 2 所示。

由于获得 FPGA 架构性能通常需要较长时间, SAMT 采用半监督方式获得需要学习的FPGA 架构。从有限的具有性能的 FPGA 架构设计空间中挑选合适的 FPGA 架构,并预测其性能。SAMT 对这 2 部分获得性能的 FPGA 架构学习,构建 FPGA 性能模型。这样,一方面使 SAMT 具有较充足的 FPGA 架构进行模型训练,另一方面减少 FPGA 性能建模时间成本。

#### 1.3 SAMT 算法实现

算法 1 呈现了 SAMT 算法实现伪代码。从 FPGA 架构设计空间中选择一部分架构,通过 VTR<sup>[8]</sup>获得这部分架构的性能,将架构与其对应 的性能组合形成标记的 FPGA 架构集。将标记

Fig.1 Scheme of the AdaBoost algorithm 图 1 AdaBoost 算法机制

Fig.2 Process of SAMT modeling

图 2 SAMT 建模过程

架构集的 2/3 作为训练集 T, 其余 1/3 作为验证集 V。 FPGA 设计空间中的其余 FPGA 架构作为未标记集 U(即没有性能结果的 FPGA 架构集),并从 U 中选择一部分作为未标记池 Q。

算法 1 SAMT 算法伪代码

准备数据:

T: 训练集; V: 验证集;  $T_{\text{add}}$ : 选择集; U: 未标记集; Q: 未标记池; I: 弱学习器数目;  $\varepsilon$ : 误差率;

β: 权重更新系统; φ: 权重更新阀值;  $D_{(i)}$ : 样本权重分布, 初始权重  $D_{(i)}=1$ ;

L<sub>1</sub>,L<sub>2</sub>: 模型树叶端最小样本数目

Begin

$T_1 \leftarrow T; T_2 \leftarrow T$

用T和L训练模型树:  $m_1 \leftarrow M5P(T_1, L_1); m_2 \leftarrow M5P(T_2, L_2)$

repeat

$m_1/m_2$ 从 U 中为彼此挑选最佳的未标记样本,对其进行标记后,加入到  $T_2/T_1$  中,同时将挑选的未标记样本加入  $T_{\rm add}$

until  $m_1/m_2$  预测 V 的精确度小于预设精确度值

$T \leftarrow T + T_{add}$

for(*t*=0; *t*<*I*; *t*++)

$m_t \leftarrow M5P(T,L_1), T 具有权重分布 <math>D_t(i)$

計算

$$\varepsilon_i = \sum_{i:\left|\frac{m_t(x_i) - y_i}{y_i}\right| > \phi} D_t(i), \quad \beta_t = \left(\frac{\varepsilon_t}{\sum_i D_t(i)}\right)^2$$

权重更新  $D_{t+1}(i) = \frac{D_t(i)}{Z_t} \begin{cases} \beta_t, \left|\frac{m_t(x_i) - y_i}{y_i}\right| \leqslant \phi \end{cases}$

输出

$$m(x) = \frac{\sum_{t} \log(1/\beta_t) \times m_t(x)}{\sum_{t} \log(1/\beta_t)}$$

end

基于训练集 T,使用  $M5P^{[9]}$ ,一种改进的模型树算法,构建 2 个不同的 FPGA 性能模型树  $m_1$ 和  $m_2$ 。 $m_1$  从未标记池 Q 中挑选最合适的未标记 FPGA 架构,这个架构需要  $m_1$  对其预测性能,加入到  $m_1$  对应的样本集之后,训练得到的新模型比  $m_1$  具有更好的预测精确度。 $m_1$  对这个最合适的未标记架构进行标记,并放入  $m_2$  对应的样本集  $T_2$ 中,同时将其放入半监督样本集  $T_{add}$ 中。 $m_2$  重复上述过程。一次交叉挑选过程中,如果都找不到最合适的未标记架构,则未标记池 Q 清空,从未标记集 U 中随机选择未标记 FPGA 架构填充新的未标记池。重复上述交叉选择过程,直到  $m_1$  和  $m_2$  具有较高的预测精确度。将训练集 T 和半监督样本集  $T_{add}$  组合形成扩充的标记训练集 T ,用 T AdaBoost 模型树算法训练 T 个弱模型树。每次学习得到的模型对 T 进行预测,如果预测其中某个 T FPGA 架构的性能误差大于 T ,则提高该 T FPGA 架构的权重,使得下一次模型训练中,对这个预测误差较大的 T FPGA 架构加强学习。最后对 T 个弱模型树加权组合,得到最终的 T FPGA 架构性能模型。

#### 2 实验验证及分析

#### 2.1 实验环境及设置

本节进行了一系列实验验证提出方法的有效性。在基于查找表的 SRAM 型 FPGA 的背景下,选取规模较大的 VTR 电路集<sup>[8]</sup>作为实验电路,并采用 VTR 获得实验电路在 FPGA 架构上的实现性能,以获得具有性能结果的 FPGA 架构。

从含有百万 FPGA 架构的架构设计空间中选择 50 个 FPGA 架构,通过 VTR 获得各实验电路在各个架构上的 实现性能。将获得性能的 50 个架构的一半用作训练集,1/4 用作验证集,1/4 用作测试集。平均相对误差(MRE) 被选作评估指标,评价提出方法构建的 FPGA 架构性能模型的预测精确度,其定义如下:

$$MRE = \frac{1}{N_t} \sum_{i=1}^{N_t} \left| \frac{y_i^* - y_i}{y_i} \right|$$

(1)

式中:  $y_i$ 表示通过 VTR 获得的 FPGA 架构的性能;  $y_i^*$ 表示性能预测模型预测的 FPGA 架构性能;  $N_i$ 则表示测试集中的 FPGA 架构数目。

#### 2.2 SAMT 对 FPGA 架构性能预测能力

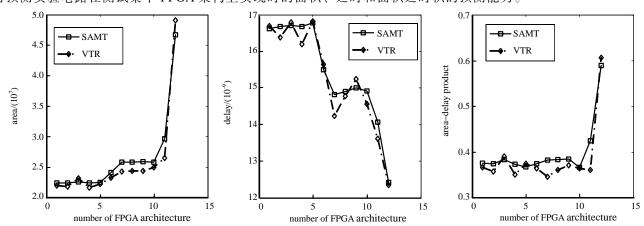

基于训练集中 25 个获得性能的 FPGA 架构,以及验证集中的 15 个 FPGA 架构, SAMT 从 FPGA 架构设计空间选择合适的未获得性能的 FPGA 架构构建 FPGA 性能模型。用获得的性能模型对测试集中的 FPGA 架构性能进行预测,并与测试集中的 FPGA 架构通过 VTR 获得的性能进行比较。图 3 展示了 SAMT 训练的 FPGA 性能模型对预测实验电路在测试集中 FPGA 架构上实现时的面积、延时和面积延时积的预测能力。

Fig.3 Predicted accuracy of SAMT performance model 图 3 SAMT 性能模型预测精确度

从图 3 可以看出,SAMT 训练的 FPGA 性能模型预测的性能结果与 VTR 实际获得的性能结果比较吻合。在预测面积时,SAMT 模型与 VTR 实际性能结果之间的最大相对误差为 6.3%,最小相对误差仅为 1%;在预测延时时,SAMT 模型的预测相对误差最大为 4.1%,最小为 0.4%;预测面积延时积时,最大相对误差为 6.62%,最小相对误差为 1.55%。可见,SAMT 能以较高的精确度预测 FPGA 架构性能。此外,在预测延时时,SAMT 预测精确度相较于预测面积和面积延时积时要高。这是因为实验电路在不同 FPGA 架构上实现时,延时结果取值较为集中,使得延时性能更好预测。

#### 2.3 预测精确度比较

本文提出的 SAMT 方法采用 AdaBoost 方法,通过对多个弱模型树的加权训练,最终获得预测能力较强的 FPGA 性能模型。下面对本文提出方

Table1 Comparison on prediction accuracy among SAMT, M5P and SMT

| method - |       | MRE   |                    |

|----------|-------|-------|--------------------|

| method – | area  | delay | area-delay product |

| SAMT     | 4.42% | 1.63% | 5.06%              |

| M5P      | 7.27% | 1.88% | 7.98%              |

| SMT      | 5.96% | 2.70% | 7.62%              |

法与传统模型树方法(M5P)以及 SMT 方法的性能预测能力进行比较。将这 3 种方法训练得到的性能模型预测结果均与 VTR 结果进行比较,获得 3 种方法的预测 MRE 如表 1 所示。

表 1 结果显示,与 M5P 方法以及 SMT 方法比较,本文提出方法 SAMT 能更好地预测 FPGA 性能。与 M5P 方法比较,SAMT 将预测精确度最高提升 39%;与 SMT 方法比较,SAMT 预测精确度最高提升 40%。上述结果说明,本文提出方法中采用的 AdaBoost 算法能够有效提高最终生成的预测模型的预测精确度。

#### 2.4 模型训练时间比较

表 2 对 SAMT,M5P 和 SMT 3 种方法的 FPGA 性能模型 训练时间进行了对比。

从表 2 可以看出, SAMT 和 SMT 的模型训练时间都要

Table2 Comparison on model training time

SAMT

M5P

SMT

training time/ms

292 953

94

130 890

表 2 模型训练时间对比

比 M5P 时间长,这是因为上述 2 种方法都是在 M5P 方法的基础上开发的,这 2 种方法需要通过初步获得的性能模型选取可利用的未获得性能的 FPGA 架构进行学习,从而提高最终获得模型的预测精确度。而且,SAMT 虽然训练多个弱学习器进行加权学习,但其时间开销并没有大幅增长,SAMT 模型训练时间不超过 5 min。

#### 2.5 SAMT 算法中参数探索

SAMT 算法中引入 2 个参数 I 和  $\phi$  ,分别代表 AdaBoost 建模过程中学习的弱模型数目和权值更新阈值。下面对这 2 个参数对最终模型精确度的影响进行评估。

表 3 以面积预测模型为例,研究了权值更新阈值对性能模型预测精确度的影响。权值更新阈值确定了在迭代学习弱学习器的过程中,哪些FPGA 架构需要加强学习。如果这个阈值设置过

表 3 权值更新阈值对性能模型预测精确度的影响

| Table3 Effect of weight updating threshold on performance model accuracy |       |       |       |       |        |  |  |

|--------------------------------------------------------------------------|-------|-------|-------|-------|--------|--|--|

| φ                                                                        | 0.02  | 0.03  | 0.05  | 0.10  | 0.20   |  |  |

| MRE                                                                      | 4.40% | 4.40% | 5.15% | 4.90% | 12.20% |  |  |

表 4 弱模型数目对性能模型预测精确度的影响

| Table4 Effect of | f the number of | weak models o | n performance | model accuracy |

|------------------|-----------------|---------------|---------------|----------------|

| I                | 2               | 5             | 8             | 20             |

| MRE              | 1.69%           | 1.63%         | 1.62%         | 1.60%          |

大,表示学习器可接受的误差范围变大,导致训练的学习器精确度不高。但是阈值的调节也并非能一直改善性能模型的预测精确度,如表 3 所示,当阈值设为 0.02 时,对性能模型的预测精确度没有影响。

训练的弱模型数目对延时模型的影响在表 4 中显示。可见,弱模型数目的增加对性能模型预测能力的改善有限,如果过多地增加弱模型的数目,反而会增加模型训练时间。因此,应该选择适宜的弱模型数目。

#### 3 结论与展望

本文提出一种半监督自适应增强模型树算法用于对 FPGA 架构性能进行表征。将 AdaBoost 算法与模型树算法相结合,并通过半监督的学习方式,训练多个加权模型树,有效地提高了算法构建的 FPGA 架构性能模型的预测精确度。实验结果证明,本文提出方法所构建的 FPGA 性能模型在预测电路在 FPGA 架构上实现的面积、延时和面积延时积时,预测精确度可达 4.42%,1.63%和 5.06%,同时能保持较少的模型训练时间开销。因此,本文提出方法可用在 FPGA 设计初期,探索高效的 FPGA 架构设计空间。

本文提出的方法不限于对基于查找表的 SRAM 型 FPGA 架构性能建模,未来还将利用该方法对基于与非锥 (And-Inverter Cone, AIC)的 SRAM 型 FPGA<sup>[10]</sup>以及 SOI(Silicon-On-Insulator)工艺的 FPGA<sup>[11]</sup>架构性能进行建模,用以高效探索 FPGA 设计空间。

#### 参考文献:

- [1] DAS J,LAM A,WILTON S J E, et al. An analytical model relating FPGA architecture to logic density and depth[J]. IEEE Transactions on Very Large Scale Integration(VLSI) Systems, 2011,19(12):2229-2242.

- [2] YANG Liqun, YANG Haigang, LI Wei, et al. A semi-supervised modeling approach for performance characterization of FPGA architectures [C]// 24th International Conference on Field Programmable Logic and Applications. Munich, Germany: IEEE, 2014:1-6

- [3] SCHAPIRE R E. The strength of weak learnability[J]. Machine Learning, 1990,5(2):197-227.

- [4] FREUND Y. Experiment with a new boosting algorithm[C]// The 13th International Conference on Machine Learning. Bari, Italy:[s.n.], 1996:148-156.

- [5] FREUND Y,SCHAPIRE R E. A decision-theoretic generalization of on-line learning and an application of boosting[J]. Journal of Computer and System Sciences, 1997,55(1):119-139.

- [6] SOLOMATINE D P,SHRESTHA D L. AdaBoost.RT:a boosting algorithm for regression problems[C]// IEEE International Joint Conference on Neural Networks. [S.l.]:IEEE, 2004:1163-1168.

- [7] WU X,KUMAR V,QUINLAN J R,et al. Top 10 algorithms in data mining[J]. Knowledge and Information Systems, 2007, 14(1):1-37.

- [8] ROSE J,LUU J,YU C W,et al. The VTR project:architecture and CAD for FPGAs from Verilog to routing[C]// The 20th ACM/ SIGDA International Symposium on Field Programmable Gate Arrays. Monterey, CA, USA:[s.n.], 2012:77-86.

- [9] WANG Y, WITTEN I. Inducing model trees for continuous classes[C]// Proceeding of European Conference on Machine Learning Poster Papers. Prague, Czech Republic: [s.n.], 1997:128-137.

- [10] ZGHEIB G,YANG Liqun, HUANG Zhihong, et al. Revisiting and-inverter cones[C]// Proceedings of the 2014 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays. Monterey, CA, USA:[s.n.], 2014:45-54.

- [11] 范斌,常青. 基于DSP的FPGA动态重构系统研究与设计[J]. 太赫兹科学与电子信息学报, 2010,8(2):123-127. (FAN Bin,CHANG Qing. Design and verification of radiation-hardened by SOI-based FPGA[J]. Journal of Terahertz Science and Electronic Information Technology, 2010,8(2):123-127.)

#### 作者简介:

**杨立群**(1989-), 女,哈尔滨市人,博士,主要研究方向为 FPGA 架构开发、FPGA CAD 工具开发.email:rachelyanglq@126.com.

**孙嘉斌**(1982-),男,山东省青岛市人,助理研究员,博士,研究方向为大规模集成电路设计.

**李** 威(1983-), 女,黑龙江省大庆市人,助 理研究员,博士,研究方向为大规模集成电路设计。

黄志洪(1983-), 男, 福建省莆田市人, 助理研究员, 硕士, 研究方向为大规模集成电路设计.

**杨海钢**(1960-),男,江苏省武进市人,研究员,博士生导师,研究方向为数模混合信号集成电路设计,超大规模集成电路设计.

### 第三届新型光电探测技术及其应用研讨会

光电探测技术是现代信息获取的主要手段之一,光电探测技术的发展是随着其他关键技术的发展而发展的,由于激光技术、 光波导技术、光电子技术、光纤技术、计算机技术的发展,以及新材料、新器件、新工艺的不断涌现,光电探测技术取得了巨大 发展。近年来,光电探测技术引起了业内人士的普遍关注,在军事和民用领域占有越来越重要的地位。

继前两届新型光电探测技术及其应用研讨会成功召开之后,应广大专家和代表要求,组委会将于2016年11月在西安市继续举办"第三届新型光电探测技术及其应用研讨会",深入研讨近年来涌现出的各种新型探测技术,包括微光探测、偏振探测、量子探测、单光子探测技术等。以促进我国新型光电探测技术及相关产业的可持续、健康发展。诚挚欢迎国内外相关领域的科研人员、教师、研究生等踊跃投稿。

主办单位: 国家自然基金委员会 中国工程院信息与电子工程学部 中国光学工程学会 微光夜视技术重点实验室

承办单位: 中国光学工程学会 中国宇航学会光电技术专业委员会 红外与微光技术应用产业联盟

联办单位:北京仿真中心 北京理工大学 长春理工大学

## 征文方向:

- 紫外探测技术及应用

- 微光探测技术及应用

- 单光子探测技术及应用

- 红外探测技术及应用

- 太赫兹探测技术及应用

- 激光探测技术及应用

- 可见光探测技术及应用

- 偏振探测技术及应用

- 量子探测技术及应用

- 多光谱/高光谱/超光谱探测技术及应用

- 复合探测技术及应用

- 空间探测技术及应用

- 信号处理与检测

- 其他应用

**论文发表:** 投稿请登录: http://events.kjtxw.com/tougao/1426493004.html, 中英文兼收。

请作者登录网站提交论文全文,组委会请专家进行审稿。通过审查的稿件被大会录用。择优推荐到正式出版物发表。英文稿件,将被SPIE会议论文集(EI检索)收录。中文稿件推荐至《红外与激光工程》(EI)、《光学精密工程》(EI)、《强激光与粒子束》、《中国光学》(科技核心期刊)、《太赫兹科学与电子信息学报》(科技核心期刊)正刊出版。

投稿截止时间: 2016年9月30日

**组委会联系方式:** 秘书处联系人: 刘 艳 电子邮箱: liuyan@csoe.org.cn 联系电话: 022-58168510