# System Design and Implementation of High-Speed Storage Based on File Management \*

ZHANG Min, MENG Lingjun\*

(National Key Laboratory for Electronic Measurement Technology North University of China, Taiyuan 030051, China)

**Abstract:** With the rapid development of storage equipment, intelligent, high-speed and miniaturization were breakthrough core technology. By adding the file management mode, the high speed storage system was designed. To improve the data transmission bandwidth, the Ethernet interface was used to receive multi-channel data in the meantime. In order to ensure that the storage module can continue to be stored after recharging, the operation address of the storage can be updated in real time. When reading data, using high speed serial port improved reading speed. The results show that the data write speed of single flash is 75 Mbyte/s. The reading speed of the upper computer is 384 Mbit/s, and the stored file is read out to the data file. It is concluded that the system is of high accuracy and practicability, and the equipment tends to be miniaturized.

Key words: network interface; electronic document; power down protection; high-speed storage

EEACC: 6150: 7210G: 1265D

doi:10.3969/j.issn.1005-9490.2020.01.030

## 基于文件管理的高速存储系统的设计与实现\*

张 敏.孟令军\*

(中北大学电子测试技术国防科技重点实验室,太原 030051)

摘 要:随着存储设备的高速发展,智能化、高速化、小型化成为不断突破的技术核心。通过增加文件管理模式,设计了高速存储系统。为提高数据传输带宽,使用以太网接口,同时接收多路数据。为保证存储模块重新上电之后可以继续存储通过实时更新存储的操作地址。数据读取时,使用高速串口,提高读出速度。测试结果表明,Flash 阵列的数据写入速度为75 Mbyte/s。上位机读取速度为384 Mbit/s,将存储的文件以 data 文件读出。可见系统准确性高、实用性强,且设备趋向小型化发展。

关键词:网络接口:文件管理:掉电保护:高速存储

中图分类号:TM938.6

文献标识码:A

文章编号:1005-9490(2020)01-0147-05

存储测试技术是能够实时完成信息的快速采集与记录,在回收后再现测试信息并由计算机处理的一种动态测试技术[1]。

随着电子技术的快速发展,信息的高速记录成为一项重要的功能。网络传输具有通信速度快、信息量大等特点。接口方式不再选用低速串口进行数据传输,转向网络接口,提高了传输带宽。在高速存储系统中,文件管理技术的实现变得尤为重要,直接影响了存储系统的数据可靠性。为了满足高速存储系统的设计需求,提出了一种适用于 Flash 存储阵列的高速存储系统的方式,极大地提高了数据索引

速度和管理效率[2]。

文件系统的实现,建立在掉电之后保存当前记录地址的基础之上,为下次记录提供一个连续的地址。为循环记录提供了可能,将记录的数据读取之后,即使没有擦除存储器也可以循环使用,存储器保留最新的数据。

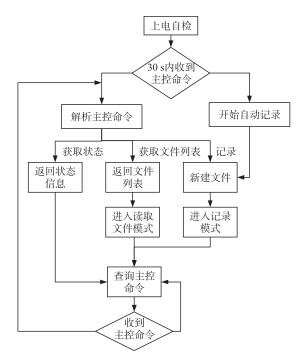

## 1 系统总体设计

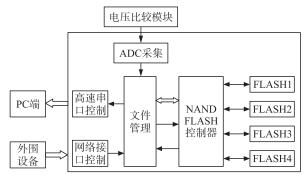

数据采集模块由 W5300 实现,通过网络接口可实现多路数据接收,FPGA 将采集的数据按照格式统一进行编帧,处理后的数据发送给 Flash 存储阵

列并进行数据备份处理。待存储设备回收,数据信息通过高速数据传输发送到上位机。系统总体设计如图 1 所示。

图 1 系统总体设计

## 2 硬件设计

#### 2.1 网络传输

网络接口具有使用方便、开发难度较小、传输距 离远、标准化接口协议、与计算机具有良好的兼容性 等特点<sup>[3]</sup>。

在设计硬件电路时, W5300 芯片体积小, 内部集成了10/100M 自适应的以太网控制器, 支持自动握手和信号线自动检测功能。包含8个可同时独立工作的端口,接收多个IP端的数据<sup>[4]</sup>。在内部锁相环最高时钟输出频率为150 MHz的情况下,可实现最大网络通信速率为50 M。整个器件采用+3.3 V单电源方式供电,通过内部电压调节器产生+1.8 V电压为内核供电<sup>[5]</sup>。

W5300 可以实现 TCP、UDP、IPRAW、和 MACRAW 等协议的网络数据通信。TCP 协议是一种报文通信协议,主要应用于互联网传输,需要建立端口连接,协议复杂,传输效率低<sup>[6]</sup>。UDP 通信是一种无连接的通信协议,UDP 发送和接收数据不需要像TCP 通信那样建立端口连接,协议简单,传输效率高,可以同多个已知的 IP 地址和端口号进行端对端通信<sup>[7]</sup>。因此设计方案采用了 UDP 协议。

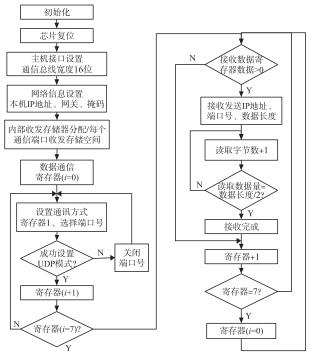

网络接口同时接收多路数据,并以端口循环扫描的方式实现数据传输。当一路数据接收完成时,会跳向下一个端口读取数据,即使每个端口的数据周期和数据长度均不同,通过访问接收寄存器查询数据量,读取接收 FIFO 的数据。当完成 8个端口的数据接收后,继续从端口 1 重新进行数据接收,采用这样轮询的方式直到数据全部接收完成。

网络接收数据具体流程图 2 所示。

图 2 网络数据接收流程

### 2.2 掉电保护

为保持电池瞬间断电时不间断给电路模块供电,采用一个 0.01 F 的"超级电容"与 DC/DC 模块并联,就可以保证 20 mA 的电路模块正常工作 100 ms 以上,完成数据存储<sup>[8]</sup>。在电源接入电路后就通过一个电阻给电容充电,控制充电电流,在电阻上要消耗一部分能量,电容上只能保持部分能量,电池的容量要比不接入超级电容时选得大一些。此外,为避免电容电流反灌,在电容前应采用防反流的保护二极管。将电池并联一个较大容值的电容,试验之前对电容充电,这样电容会对电池的瞬时断电或电压波动起到一定的补偿作用。

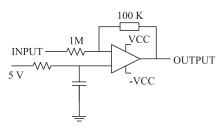

根据 NAND Flash 存储芯片的数据手册查看得到如下数据:页编程的最长时间为 500 μs,选择合适的 DC/DC 模块,前提是,存储的电量要满足写一页数据的时间,因此,前端通过设置电压比较器,如图所 3 所示。

图 3 电压比较模块

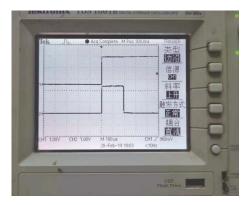

当电压低于 2.5 V 时,启动停止信号,此时,记录器进行当前数据地址的记录,示波器抓到的图像

显示如图 4 所示。

图 4 示波器显示

从图 4 可以看出,第 1 根信号线是电压比较后的信号持续时间,第 2 根信号线是进行页操作需要的 200 μs 页操作时间,因此,该掉电模块足以保护了文件信息的编写。

## 3 数据存储设计

#### 3.1 DMA 数据传输

采集数据后进行数据编帧,增添时间码和数据帧头以区分数据类型,时间码由 FPGA 内部标准时钟产生,以接收数据的最小周期为单位。将数据与时间建立关系可追溯不同时刻各设备的具体参数的变化情况,便于回收后,精准地分析数据。由于传输的数据容量大且速度快,采用 DMA 数据传输方式向存储阵列发送数据。

在加载数据时,采用 DMA 的方式进行传输, Flash 编程以页为单位,每页可写入的数据量为 4 096 byte<sup>[9]</sup>。通常在进行页编程时,状态机根据时 钟上升沿将数据写入,每写一个数据需要 3 个状态, 这样写一页就需要循环 4 096×3=12 288 个状态,为 节省时间选用 DMA 的方式,使得系统满足速度的 要求。当前端 FIFO 缓存的数据量大于 4 096 byte 时,将写信号切换到 50 MHz,计数器从 0 开始计数, 累加到 4 095 时,Flash 控制器关闭前端缓存的读使 能,计数器清零,同时将写信号切换为正常受 Flash 控制器控制的状态。

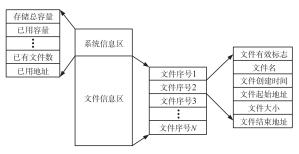

#### 3.2 文件管理

存储系统采用 Flash 阵列的方式进行数据管理,在数据存储中,为了提高空间管理效率避免存储碎片的产生,以页为最小存储单位,也就是在记录和数据读数中按页来分配空间<sup>[10]</sup>。建立地址映射列表查找对应的地址。

存储数据以文件的方式归档,本次的记录时间,记录次数,开始地址、结束地址,存储的数据量。每

图 5 文件管理模式

次读取数据时,首先将存储的文件内容读取出来,通过文件记录的信息,查看存储器做的试验次数以及每次的存储量,显示剩余存储量,判断是否需要擦除数据。同时,提供了文件数据备份功能,一旦数据读写错误或者损伤,可以通过备份数据恢复原有的数据,文件索引表采用冗余设计以保证数据的完整性与连续性。

每次记录数据时,通过检索文件列表,查找相对 应地址数据,记录结束时通过在文件索引表中添加 新的文件信息。同时,当系统突发性断电,为保证下 一次的准确记录,通过检测掉电信号,是否添加新的 文件信息,实现掉电防御机制。不仅提高了读取数 据的准确性,简化了人员的操作及流程,趋向于智能 化管理。从硬件系统实现了对数据的分类管理,为 数据内部检索提供便利。

#### 3.3 循环记录

存储模块实现循环记录,地址存储空间每次读写操作之后都会更新当前地址,更新的地址被存入指定的地址空间中,在下一次记录数据开始之前,将上次存入的地址读出,页地址加1之后作为此次工作的开始地址,这样就可以保证每次在重新上电之后,操作地址可以再次从 Flash 的地址存储空间中读出,从而继续工作。在存储器记录数据时,按照芯片的 plane0 到 plane7 依次存储当一个 plane 的容量存满之后,可以自行切换到另外一个 plane 继续工作,对于每次操作都涉及的操作地址包含块地址以及页内地址,这样可以提高存储器的使用寿命,提高

了可靠性。

## 4 系统测试和数据分析

#### 4.1 文件存储测试

读取数据之前,首先将存储器内部的文件信息读取出来,文件信息传输内容如图 6 所示。选择记录的次数,通过查询文件信息,得到记录数据量,便于设置读取量。从文件列表中观测可知:存储文件名为"当前时间",存储起始时间为"2018 年 5 月 6 日 20 点 09 分",存储文件长度为 1.5 Mbyte,存储位置是从第 0 块到第 2 块,如图 7 所示。

图 6 文件信息表

图 7 文件信息

#### 4.2 数据分析

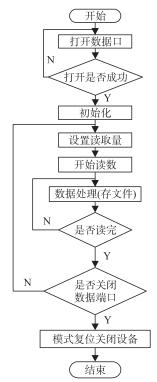

数据传输,采用高速串口 FT600,使用 USB3.0 标准接口,最大传输速度可达 5 Gbyte/s,兼容 USB2.0 接口。FT600 是双通道多功能的 USB 传输 芯片,芯片内部发送缓存和接收缓存均为 16 kbyte<sup>[11]</sup>。可以工作在多种接口模式下,其中 FT245 同步模式能达到的最大速度是 100 Mbyte/s。

FT600 在外部接上 EEPROM 以保存芯片的配置信息。选择串口作为数据传输,也是为了配合上位机软件的设计通过使用 D3XX 驱动,可以很方便用于软件调用器内部函数<sup>[12]</sup>。

数据传输的流程图 8 所示。

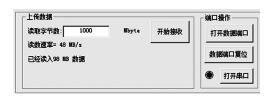

将读出的数据进行帧格式检测,由于存储的多路数据是按照一定的帧格式发送,通过数据分离,并对帧格式以及时间计数进行连续性检测去判断接收到的数据的准确性。经实测数据上传速度可以达到384 Mbit/s。传输速度受前端存储器内部读出速度的影响,但也满足数据上传的要求。上位机显示界面如图 9 所示。

图 8 上位机数据传输流程

图 9 上位机显示界面

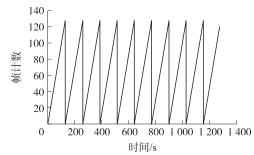

通过靶场实际测试,数据读取时,读完一页添加一个页分隔符以及页计数,使用 MATLAB 进行解析提取页计数,并用波形图画出,波形如图 10 所示。通过提取时间码,判断数据连续性,得到数据包的丢失情况。实验结果表明数据存储完整,采集的数据完整无丢失,数据读取时,页计数连续,数据无丢失,UART 传输可靠。

图 10 帧计数波形图

## 5 结论

本文设计了一种高宽带且智能化的存储器设备, 通过网络接口接收多个设备的数据,节省了设备的机 械空间,趋于小型化发展,并实现了存储数据的电子 文件归档,数据循环记录以及设备防掉电的设定,产品向数据智能化方向发展,同时单片 Flash 的读写达到高速,在大容量存储领域中,有了先决条件,具有广泛的应用价值,并且成功应用在飞行器设备中。

#### 参考文献:

- [1] 张洪柳,张春.一种可编程多路闪存控制器的设计与验证[J]. 电子技术应用,2017(9):39-42.

- [2] 高加琼,魏霖静. 嵌入式中 flash 存储设备日志冗余管理[J]. 控制工程,2017,24(6);1241-1247.

- [3] Qin Z, Wang Y, Liu D, et al. Real-Time Flash Translation Layer for NAND Flash Memory Storage Systems [J]. IEEE Transactions on Multi-Scale Computing Systems, 2016;2(1):17-29.

- [4] 徐玉杰. 高速大容量存储系统的设计与实现[D]. 陕西: 西安电子科技大学,2014.

- [5] 李大伟,刘成,郑建华,等. 适用于探空火箭的图像采集与压缩系统[J]. 国防科技大学学报,2017,39(2):71-77.

- [6] 张威. 基于 FPGA 的高速以太网接口设计和实现[D]. 四川: 电子科技大学,2016.

- [7] 倪有粮. 基于 FPGA 的以太网 MAC 层研究[D]. 浙江:浙江工业大学,2016.

- [8] 马崇鹤,赵凤军,冯杰. 雷达系统高速大容量 Flash 存储器平台管理的设计和应用[J]. 电子器件,2016,39(6):1407-1415.

- [9] 孙昕, 张世海. 基于 FPGA 的水下数据存储系统设计[J]. 计算机与数字工程,2016,44(4):767-771.

- [10] 方宏. 电子文件管理系统的设计与实现[D]. 武汉:湖北工业大学, 2016.

- [11] 谢艺平. 固态硬盘存储管理及数据恢复探讨[D]. 长沙:湖南大学,2016.

- [12] Sutikno T A, Mochammad F. Bulletin of Electrical Engineering and Informatics [J]. Universitas Ahmad Dahlan, 2012;57-58.

**孟令军**(1969-),汉族,山东青岛人,中 北大学副教授,硕士生导师,主要研究 方向为数字图像处理技术、动态测试 存储技术,3037559350@qq.com。