| 面向处理器功能验证的硬件化SystemVerilog断言设计 |

| |

| 引用本文: | 张子卿, 石侃, 徐烁翔, 王梁辉, 包云岗. 面向处理器功能验证的硬件化SystemVerilog断言设计[J]. 计算机研究与发展, 2024, 61(6): 1436-1449. DOI: 10.7544/issn1000-1239.202331003 |

| |

| 作者姓名: | 张子卿 石侃 徐烁翔 王梁辉 包云岗 |

| |

| 作者单位: | 1.处理器芯片全国重点实验室(中国科学院计算技术研究所) 北京 100190;2.中国科学院大学计算机科学与技术学院 北京 100049;3.上海科技大学信息科学与技术学院 上海 201210;4.中国科学技术大学 计算机科学与技术学院 合肥 230027 |

| |

| 基金项目: | 国家重点研发计划项目(2023YFB4405105);中国科学院计算技术研究所创新项目(E261100);国家自然科学基金重大项目(62090023)~~; |

| |

| 摘 要: |

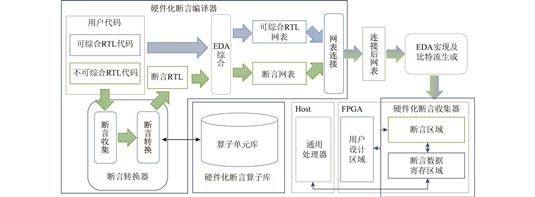

功能验证在处理器芯片开发流程中所占用的时间超过70%,因此优化提升功能验证环节的效率非常必要. 软件仿真等传统验证方法提供了包括断言等多种验证机制,以提升验证的细粒度可见性和自检查能力,但是软件仿真运行速度较慢,在高效性方面有明显不足. 基于FPGA的硬件原型验证方法能极大地加速验证性能,但其调试能力较弱,虽能快速发现漏洞,但难以定位漏洞出现的具体位置和根本原因,存在有效性不足难题. 为同时解决上述功能验证有效性与高效性的问题,提出一种将不可综合的断言语言SVA(SystemVerilog Assertion)自动转换成逻辑等效但可综合的RTL电路的方法,聚焦于断言这一类对设计进行非全局建模、纵向贯穿各抽象层级的验证方式,对基于全局指令集架构(instruction set architecture, ISA)模型的验证能力进行补足.

同时,结合FPGA细粒度并行化、高度可扩展的优势,对处理器的验证过程进行硬件加速,提升了处理器的开发效率. 实现了一个端到端的硬件断言平台,集成对SVA进行硬件化的完整工具链,并统计运行在FPGA上的硬件化断言的触发和覆盖率情况. 实验表明,和软件仿真相比,所提方法能取得超过2万倍的验证效率提升.

|

| 关 键 词: | 断言 处理器验证 硬件仿真 现场可编程逻辑门阵列 原型验证 |

| 收稿时间: | 2023-12-14 |

| 修稿时间: | 2024-03-22 |

|

| 点击此处可从《计算机研究与发展》浏览原始摘要信息 |

|

点击此处可从《计算机研究与发展》下载免费的PDF全文 |

|