| FPGA硬核处理器系统加速数字电路功能验证的方法 |

| |

| 引用本文: | 刘小强, 袁国顺, 乔树山. FPGA硬核处理器系统加速数字电路功能验证的方法[J]. 电子与信息学报, 2019, 41(5): 1251-1256. doi: 10.11999/JEIT180641 |

| |

| 作者姓名: | 刘小强 袁国顺 乔树山 |

| |

| 作者单位: | 1.中国科学院微电子研究所 北京 100029;;2.中国科学院大学 北京 100049 |

| |

| 摘 要: |

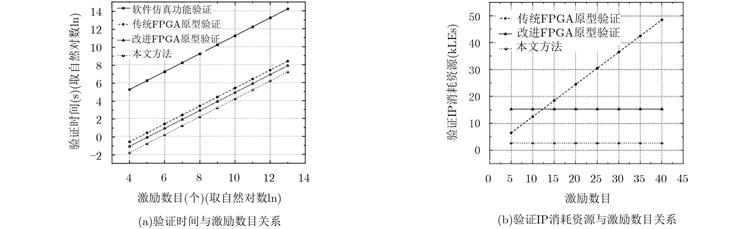

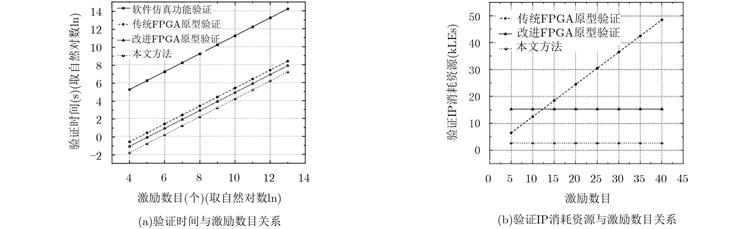

为了缩短专用集成电路和片上系统的功能验证周期,该文提出FPGA硬核处理器系统加速数字电路功能验证的方法。所提方法综合软件仿真功能验证和现场可编程门阵列原型验证的优点,利用集成在片上系统现场可编程门阵列器件中的硬核处理器系统作为验证激励发生单元和功能验证覆盖率分析单元,解决了验证速度和灵活性不能统一的问题。与软件仿真验证相比,所提方法可以有效缩短数字电路的功能验证时间;在功能验证效率和验证知识产权可重用方面表现优于现有的FPGA原型验证技术。

|

| 关 键 词: | 专用集成电路 功能验证 片上系统 FPGA原型验证 SoC FPGA |

| 收稿时间: | 2018-07-02 |

| 修稿时间: | 2018-01-10 |

| 本文献已被 万方数据 等数据库收录! |

| 点击此处可从《电子与信息学报》浏览原始摘要信息 |

|

点击此处可从《电子与信息学报》下载免费的PDF全文 |

|