| 波动动态差分逻辑RISC-V CPU芯核的功耗抑制技术研究 |

| |

| 引用本文: | 崔小乐, 李修远, 李浩, 张兴. 波动动态差分逻辑RISC-V CPU芯核的功耗抑制技术研究[J]. 电子与信息学报, 2023, 45(9): 3244-3252. doi: 10.11999/JEIT230211 |

| |

| 作者姓名: | 崔小乐 李修远 李浩 张兴 |

| |

| 作者单位: | 1.北京大学深圳研究生院集成微系统重点实验室 深圳 518055;;2.鹏城实验室 深圳 518055 |

| |

| 基金项目: | 深圳学科布局项目(JCYJ20220818100814033),深圳孔雀团队项目(KQTD20200820113105004),广东省重点科技研发计划项目(2019B010155002) |

| |

| 摘 要: |

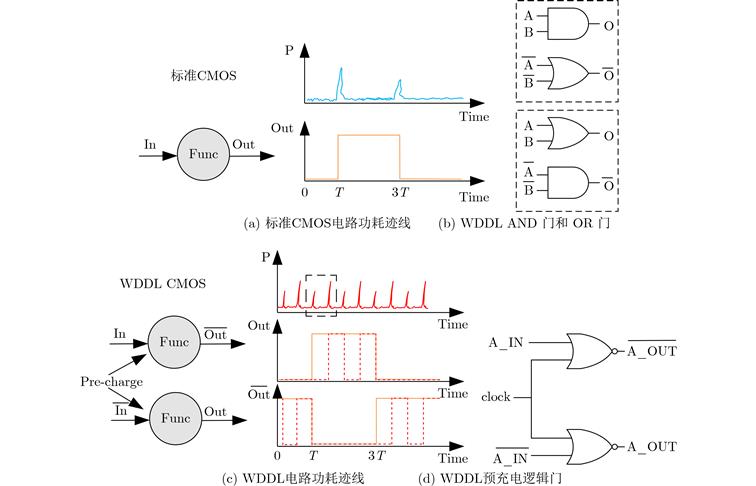

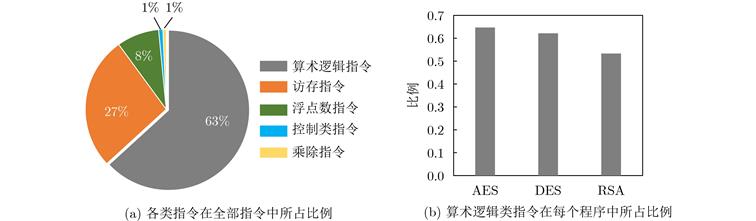

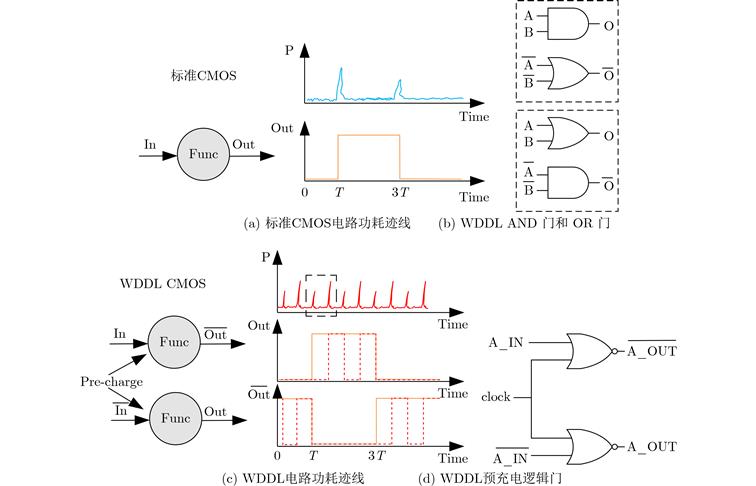

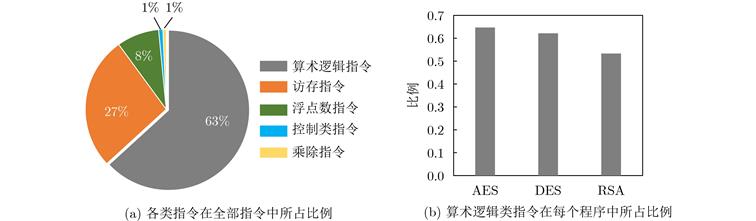

差分功耗分析(DPA)攻击不仅威胁加密硬件,对加密软件的安全性也构成严重挑战。将波动动态差分逻辑(WDDL)技术应用在RISC-V指令集的处理器芯核上可减少功耗信息的泄露。但是,WDDL技术会给电路引入巨大的功耗开销。

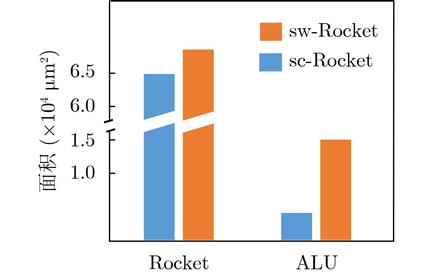

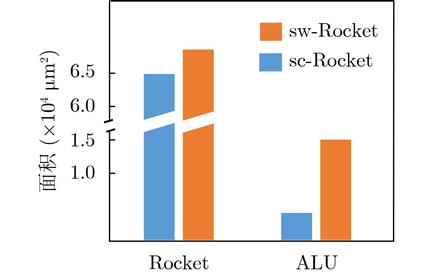

该文针对基于WDDL的RISC-V处理器芯核提出两种功耗抑制方法。虽然随机预充电使能技术与指令无关,而预充电使能指令技术需要扩充指令集,但这两种方法都是属于轻量级的设计改进。仿真结果表明,采用了随机预充电使能技术和预充电使能指令技术的Rocket 芯核的电路功耗分别是原始的WDDL Rocekt 芯核功耗的42%和36.4%。

|

| 关 键 词: | 差分功耗分析 RISC-V 芯核 波动动态差分逻辑 功耗信息泄露 功耗抑制 |

| 收稿时间: | 2023-04-23 |

| 修稿时间: | 2023-08-23 |

|

| 点击此处可从《电子与信息学报》浏览原始摘要信息 |

|

点击此处可从《电子与信息学报》下载免费的PDF全文 |

|